# 16 Bit Vedic Arithmatic& Logic Unit

### T. Swapna Rani, C.Nirmala, Srilaxmi. P

T. Swapna Rani, Asst.Professor, Dept. of ECE, CMR College of Engineering &Technology ,Hyderabad, Telangana, India(Email: tswapnarani@cmrcet.org)

C. Nirmala, Asst.Professor, Dept. of ECE, CMR College of Engineering &Technology ,Hyderabad, Telangana, India(Email: cnirmala@cmrcet.org)

Srilaxmi. P, Asst.Professor, Dept. of ECE, CMR College of Engineering &Technology ,Hyderabad, Telangana, India(Email: psrilaxmi@cmrcet.org).

Article Info Volume 81 Page Number: 6387 - 6393 Publication Issue: November-December 2019

Article History Article Received: 5 March 2019 Revised: 18 May 2019 Accepted: 24 September 2019 Publication: 28 December 2019 Abstract:

This paintings is devoted for the format and FPGA implementation of a 16bit Arithmeticmodule, which makes use of Vedic Mathematics algorithms.For Multiplication arithmetic severa Vedic multiplication techniques like UrdhvaTiryakbhyam,Nikhilam and Anurupye has been very well analysed. Also Karatsubaalgorithmformultiplication has been mentioned. It has been determined UrdhvaTirvakbhvamSutrais most green Sutra (Algorithm), giving that minimumdelayformultiplication of alltypes of numbers.UsingUrdhvaTiryakbhyam, a 16x16 bit Multiplier has been designed and the use of this Multiplier, a Logic unit unit and Shifter has been designed. Then, an Arithmetic and proper judgment module has been designed which employs those Vedic multiplier Operation and addition, subtraction, shifter and common sense gates. Logic verification of those modules has beendone via the use of Xilinx10.Three. Further, the complete format of Arithmetic module has been realised on Xilinx Spartan 3E FPGA bundle deal and the output has been demonstrated. The synthesis effects display that the computation time for calculating the made of 16x16 bits is 24.28 ns,at the same time as for the whole ALU operation 38.313 ns. Keywords: Vedic, FPGA, UrdhvaTiryakbhyam.

### I. INTRODUCTION

Number juggling is the most arranged and most unmistakable beautiful bit of calculating. The name Arithmetic begins from Greek explanation "arithmos". Number juggling is utilized by very anybody, for duties starting from direct reliably convincing work of art like checking to forefront age and business experience figurings. As a surrender end stop last thing, the prerequisite for a snappier and new Arithmetic Unit in pc structures has been a theme of recreation action over an entire arrangement. Created by craftsmanship gave in this theory, utilizes Vedic number juggling and goes all around mentioned, utilizing technique for utilizing first organizing a Vedic multiplier, by then a decision judgment unit after which at long last an ALU module which uses this multiplier and fitting judgment unit. The four basic activities in clear number juggling are improvement, subtraction, duplication and division. Addition, basically is the sensible activity of scaling a one territory with the guide of the use of technique for a few unique. Looking at these days' arranging the world over, increase based endeavors are a part of the reliably utilized Functions, after a short time finished in heaps of Digital Signal Processing (DSP) applications which joins Convolution, Fast Fourier Transform, sifting and in Arithmetic Logic Unit (ALU) of Microprocessors. Since increment is this kind of commonly utilized activity, it's principal for a

multiplier to be lively and low power green as such, improvement of a short and power multiplier has been a subject of vitality more than a few years.

Addition Accumulate or MAC assignments is relatively a generally utilized activity in various Digital sign preparing Applications. Eventually, no longer extraordinary Digital Signal Processors, yet additionally bolstered point Microprocessors merge a submitted Multiply Accumulate Unit or MAC unit. When talking about the MAC unit, the segment of Multiplier might be really sizeable as it lies inside the certainties course of the MAC unit and its development must be snappy and fit. A MAC unit joins a multiplier finished in combinational regular comprehension, as a rule with a short snake and expert be a touch of up, with deals with surrender stop result on clock.

Confining quality use and discard for virtual frameworks includes streamlining in any regard times of the course of action. This progress methodology picking the exceptional Algorithm for the situation, this being the marvelous level of relationship, by then the circuit style, the topology lastly the period used to position into effect the virtual circuits. Subordinate upon the relationship of the extra substances, there are stunning sorts of multipliers accessible. A particular multiplier shape is picked fundamentally subject to the thing.

Two most regular growth checks saw inside the impelled; equipment are bunch duplication set of benchmarks and Booth augmentation set of models. The figuring time invigorated with the guide of the obliging assistant of utilizing the pack multiplier is really a shocking group plenitude less in perspective on reality the divided thing are settled transparently in parallel. The dispose of identified with the gathering multiplier is the time considering the guide of utilizing system for the alerts to spread through the portals that from the extension appear. Corner augmentation is each remarkable noteworthy broadening set of signs. Colossal compensation locale presentations are required for over the top beat augmentation and exponential tasks which in flip require beast fractional total and halfway pass on registers. Addition of n-bit operands utilizing a radix-four pay space recording multiplier calls for about n/(2m) clock cycles to make the least huge piece of the exact opposite thing, where m is the extent of offers an area recorder snake degrees.

As an issue of first centrality, some unquestionable and essential duplication figurings have been imparted to find Computer Arithmetic from an in each pragmatic sense considered verifiably novel factor of view. By then a few Indian Vedic Mathematics checks have been imparted. In present day for Multiplication of a nbit state with each other n-bit word, n2 extensions are required. To wander this, Karatsuba Algorithm has been said which brings the duplications required, almost the whole way genuinely down to n1.Fifty 8, for n bit word. By then "Urdhvatiryakbhyam Sutra" or "Vertically and Crosswise Algorithm" for development is referenced and after that used to extend automated multiplier shape. This radiates an impression of being truly fundamentally like the exceptional show multiplier structure. This Sutra displays the most ideal approach to manage area duplication of a titanic range (N x N, of N bits each) with the beneficial pleasing associate of the utilization of breaking it into increasingly humble measures of range (N/2 = n, state) and those progressively minor numbers can again be broken into more modest numbers (n/2 each) until we gain multiplicand length of  $(2 \times 2)$ . Thusly, streamlining the entire addition approach. The duplication set of proposals is then shown to display its computational comprehended execution through bringing an occasion of chopping down aNxN-bit Multiplication to 2x2piece Multiplication activity. This depictions gives a reasonable arrangement strategy for quick and locale common digit multiplier set up together certainly totally concerning Vedic Mathematics after which a MAC unit has been utilized this multiplier. At long last the Multiplier and MAC unit in perspective on this made, had been executed in making an Arithmetic module ..

### **II. IMPLEMENTATION OF VEDIC ALU**

The proposed Arithmetic Module has first been cut up into 3 smallermodules, that is1. Multiplier, 2. Arithmetic module, three.Logic module as an entire. These modules had been made using Verilog HDL.

#### **III.VEDIC MULTIPLIER**

The design starts offevolved first with Multiplier layout, this is 2x2bitmultiplier. Here, "UrdhvaTiryakbhyam Sutra" or "Vertically and Crosswise Algorithm" for multiplication hasbeen correctly used to increase virtual multiplier shape. This set of pointers is quitedifferent from the traditional

### **IV. CONCLUSION**

CMOS Two Stage Operational Amplifier is designed and simulated in 180nm and 45nm technologies strength deliver of the form is 1. Eight V and 1 V. Respectively acquired gain in 180nm era is 59dB and in 45nm technology is 60.4dB. Power dissipation in 180nm technology is 360uW and energy dissipation in 45nm era is 123uW.Approach of multiplication, this is to add and shift the partial products. This Sutra suggests a manner to address multiplication of a bigger amount (N x N, of N bits every) with the aid of breaking it into smaller numbers of length (N/2 = n, say) and those smaller numbers can once more be damaged into smaller numbers (n2 each) till we obtain multiplicand size of  $(2 \times 2)$ . Thus, simplifying the complete multiplication manner.

For Multiplier, first the essential blocks, which may be the 2x2 bit multipliers had beenmade after which, using the ones blocks, 4x4 block has been made after which the use of this 4x4block, 8x8 bit block and then sooner or later 16x16 bit Multiplier has been made. The deviced termined on for synthesis is Device family Spartan 3E, tool is xc3s500, package deal dealdeal fg320 with speed grade -four.So permit's start from the synthesis of a 2x2 bit multiplier.

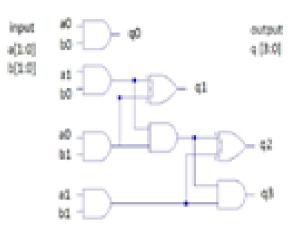

### Hardware realization of 2x2 multiplier block

The hardware realization of 2x2 multiplier blocks is illustrated inFg 3.2. For the sake of simplicity, the usage of clock and registers is not shown, but emphasis hasbeen laid on understanding of the algorithm

### 3.1.2 4x4 Bit Multiplier

The 4x4 Multiplier is made by utilizing 4, 2x2multiplier squares Here, theMultiplicands are ofbit size (n=4) where as the outcome is of 8 piece sizeThe information is brokeninto progressively humble lumps of size of n/2 = 2, for the two wellsprings of data, that is an and b. These

newlyformed bits of 2 bits are given as responsibility to 2x2 multiplier square and the outcome passed on 4 bits, which are the yield produced using 2x2 multiplier square are sent for improvement to an expansion tree, as appeared in the Fig 3.3.

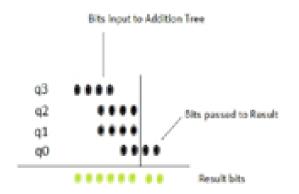

Here , instead of following progressive augmentation, the improvement tree has been changed as per Wallace tree take after the other the proportionate, consequently lessening the degrees of improvement to 2, rather than 3. Here, two lower bits of q0 pass direct to yield, while the upper bits of q0 are fortified into augmentation tree. The bits being proceeded to improvement tree can be besides depicted by the outline in Fig 3.4.

# Fig 3.4 Addition of partial products in 4x4 block

### 3.1.3 8x8 bit Multiplier

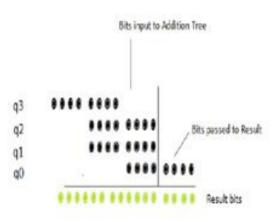

The 8x8 Multiplier is made through utilizing four , 4x4 multiplier squares. Here ,the multiplicands are of bit length (n=8) in which because of reality the last thing is of sixteen piece period. The enter isbroken into humbler bunches size of n/2 = 4, for the two data sources, that is an and b, much like as incase of 4x4 augmentation square. These starting late shaped bits of 4 bits are given as pledge to 4x4 multiplier square, wherein later these new bunches are harmed into amazingly progressively little chunksof size n/4 =2 and proceeded to 2x2 addition square. The outcome passed on, from yield of 4x4 piece addition foil this is of eight bits, are sent for improvement to an expansion tree, as appeared in the Fig three.5 under

Fig 3.5 Block Diagram of 8x8 Multiply block

# Fig 3.6 Addition of Partial products in 8x8 block

Here, one reality need to be stored in mind that, each 4x4 multiply block works as illustrated inFig three.3.In 8x8 Multiply block, lower 4 bits of q0 are surpassed immediately to output and theremaining bits are fed for addition into addition tree, as proven in Fig 3.Five. The addition ofpartial merchandise in proven in Fig three.6

### 3.2 ADDER

In general, carry ripple adders can be used when they meet timing constraints because they are compact and easy to build. When faster adders are required, carryincrement and carry skip architectures can be used, particularlyfor 8 to 16 bit lengths.Hybrids combining these techniquesare

also popular. At word lengths of 32 and especially 64 bits, tree adders are distinctly faster.Good logic synthesis tools automaticallymap the "+" operator onto anappropriate adder to meet timing constraints whileminimizing the area. For example, theSynopsysDesignwarelibraries contain carryrippleadderscarry select adders, carrylookahead adders and a variety of prefixadders.

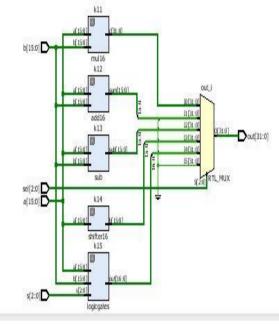

### 3.3 ALU MODULE

The ALU module designed in this work, makes use of 5 components, that are, Adder, Subtractor, Multiplier, shifter and Logic unit. A a result, the Alu unit can perform fixed Point addition, subtraction. multiplication, shifting and logic operations operationson 16 bit data. Here the inputs are Data a and Data b, which are 16 bits wide.Thealu unit uses conventional adder,shifter subtractor and logic operation, while the multiplier is made using VedicAlgorithm.The control signals whichguide the Alu unit to perform a particular operation, ie

Addition, subtraction, multiplication, shifing and logic operations using s0,s1 and s2, which are provided by the controlcircuit. Control circuit is beyond the scope of this thesis.Nowlets have a look at the status of control lines s0,s1 and s2 and the correspondingalu operation being performed.

Fig 3.10 Block Diagram of Arithmetic module

| V. | RESULTS |  |

|----|---------|--|

|----|---------|--|

| Current Simulation<br>Time: 1000 ns |      | ns 100 ns 200 ns 300 ns 400 ns 500 ns 600 ns 700 ns 800 ns 900 ns 1000 ns |  |

|-------------------------------------|------|---------------------------------------------------------------------------|--|

| 🖽 🚮 c[31:0]                         | 1    | 11602500                                                                  |  |

| 🖽 👧 a[15:0]                         | 2550 | 2550                                                                      |  |

| 🗄 🚮 b[15:0]                         | 4550 | 4550                                                                      |  |

|                                     |      |                                                                           |  |

Fig 5.1 Simulation Waveform of 16X16 vedic multiplier

| Current Simulation<br>Time: 1000 ns |   | 940 ns 945 ns 950 ns 955 ns 960 ns 965 ns 970 ns 975 ns 980 ns 985 ns 990 ns 995 ns 1000 ns |

|-------------------------------------|---|---------------------------------------------------------------------------------------------|

| 🗉 🚮 sum[16:0]                       | 2 | 27311                                                                                       |

| 🖽 🚮 a[15:0]                         | 1 | 14575                                                                                       |

| 🗄 🚮 b[15:0]                         | 1 | 12736                                                                                       |

|                                     |   |                                                                                             |

Fig 5.2 Simulation waveform of Adder

| VE       1000                       | <b>N</b> 110 |                                                                             |

|-------------------------------------|--------------|-----------------------------------------------------------------------------|

| Current Cimulation                  | 0.0          |                                                                             |

| Current Simulation<br>Time: 1000 ns |              | 0 ns 100 ns 200 ns 300 ns 400 ns 500 ns 600 ns 700 ns 800 ns 900 ns 1000 ns |

| 🗄 😽 c[15:0]                         | 50           | 50                                                                          |

| 🗄 😽 a(15:0)                         | 2500         | 2500                                                                        |

| 🛚 😽 b(15:0)                         | 50           | 50                                                                          |

|                                     |              |                                                                             |

|                                     |              |                                                                             |

Fig 5.3 Simulation waveform of Division

|                                     | 0. |                                                                             |  |  |  |  |  |  |  |  |  |

|-------------------------------------|----|-----------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Current Simulation<br>Time: 1000 ns |    | 0 ns 100 ns 200 ns 300 ns 400 ns 500 ns 600 ns 700 ns 800 ns 900 ns 1000 ns |  |  |  |  |  |  |  |  |  |

| # 🚮 a[15:0]                         | 1  | 16/b00000000011001                                                          |  |  |  |  |  |  |  |  |  |

| 🗉 🚮 b[15:0]                         | 1  | 16'50000000000001100                                                        |  |  |  |  |  |  |  |  |  |

| 🛚 😽 snot[15:0]                      | 1  | 16511111111100110                                                           |  |  |  |  |  |  |  |  |  |

| 🗉 🚮 sor[16:0]                       | 1  | 17b000000000011101                                                          |  |  |  |  |  |  |  |  |  |

| 🗉 🚮 sand[16:0]                      | 1  | 17/b000000000000000000                                                      |  |  |  |  |  |  |  |  |  |

| # 🚮 sxor[16:0]                      | 1  | 17/b000000000010101                                                         |  |  |  |  |  |  |  |  |  |

| # 🚮 sxnor[16:0]                     | 1  | 17b111111111101010                                                          |  |  |  |  |  |  |  |  |  |

| # 🚮 snand[16:0]                     | 1  | 17b11111111111111111                                                        |  |  |  |  |  |  |  |  |  |

Fig 5.4 Simulation waveform of Logic gates opration

Fig 5.5 Simulation waveform of Shifter

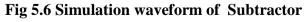

| · · · · · · · · · · · · · · · · · · · |    |      | • • -  | · .    |        |        |        |        |        |        |        |         |

|---------------------------------------|----|------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------|

|                                       | 0. | ns   |        |        |        |        |        |        |        |        |        |         |

| <b>Current Simulation</b>             |    | 0    | 100    | 000    | 000    | 100    | 500    | 000    | 700    | 000    | 000    | 1000    |

| Time: 1000 ns                         |    | 0 ns | 100 ns | 200 ns | 300 ns | 400 ns | 500 ns | 600 ns | 700 ns | 800 ns | 900 ns | 1000 ns |

|                                       |    |      |        |        |        |        |        |        |        |        |        |         |

| 🗄 👌 sub[15:0]                         |    |      |        |        |        |        | -15230 |        |        |        |        | *       |

| 🖬 😽 a[15:0]                           | 1  |      |        |        |        |        | 10254  |        |        |        |        |         |

| 🖬 😽 b[15:0]                           | 2  |      |        |        |        |        | 25484  |        |        |        |        |         |

|                                       |    |      |        |        |        |        |        |        |        |        |        |         |

## **VI. CONCLUSION**

The design of 16 bit Vedic multiplier, 16 bit Multiply Accumulate unit and 16 bitArithmetic module has been realized on Spartan XC3S500-4FG320 device.Thecomputationdelay for the MAC unit andArithmetic module are 11.151 ns and15.749 ns respectivelywhichclearly shows improvement in performance.FPGA implementation proves the hardware realization of

Vedic

MathematicsAlgorithms.UdrhvaTiryakbhayam Sutra is highly efficient algorithm for multiplication.

### **VII. REFERENCES**

- [1] Jagadguru Swami Sri Bharati Krishna TirthjiMaharaja,"Vedic Mathematics", MotilalBanarsidas, Varanasi, India, 1986.

- [2] Harpreet Singh Dhillon and AbhijitMitra, "A Reduced- Bit Multiplication Algorithm for Digital Arithmetics", International Journal of Computational and Mathematical Sciences 2;2 ©www.waset.org Spring 2008.

- [3] ShripadKulkarni, "Discrete Fourier Transform (DFT) by using Vedic Mathematics", report, vedicmathsindia.blogspot.com, 2007.

- HimanshuThapliyal, SaurabhKotiyal and M. B [4] Srinivas. "Design and Analysis of Α NovelParallel Square and Cube Architecture Based On Ancient Indian Vedic Mathematics", Centrefor VLSI and Embedded System Technologies, International Institute of InformationTechnology, Hyderabad, 500019, India, 2005 IEEE

- [5] ShamimAkhter, "VHDL Implementation of Fast NXN Multiplier Based on Vedic Mathematics", Jaypee Institute of Information Technology University, Noida, 201307 UP, INDIA, 2007 IEEE

- [6] HimanshuThapliyal and M.B Srinivas, "An Efficient Method of Elliptic CurveEncryption Using Ancient Indian Vedic Mathematics", IEEE, 2005.

- [7] El hadjyoussefwajih, ZeghidMedien, Machhout Mohsen, BouallegueBelgacem, TourkiRached,"Efficient Hardware Architecture of Recursive Karatsuba-OfmanMultiplier", 2008 on International Conference Design & IntegratedSystems Technology of in Nanoscale Era

- [8] Abhijeet Kumar, Dilip Kumar, Siddhi, "Hardware Implementation of 16\*16 bit Multiplierand Square using Vedic Mathematics", Design Engineer, CDAC, Mohali.

- [9] HimanshuThapliyal and Hamid R. Arabnia, "A Time-Area- Power Efficient Multiplier andSquare Architecture Based On Ancient Indian Vedic Mathematics", Department of ComputerScience, The University of Georgia, 415 Graduate Studies Research Center Athens, Georgia30602-7404, U.S.A.

- [10] "Spartan-3E FPGA Starter Kit Board User Guide", UG230 (v1.1) June 20, 2008.