# Implementation of ASIC Design Cycle with Different Techniques for Area and Power

P. Venkanna<sup>1</sup>, K. Vineetha<sup>2</sup>, C. Laxmi Kanth Reddy<sup>3</sup>

<sup>1,3</sup>AssistantProfessor, Malla Reddy Institute of Technology, Hyderabad, India <sup>2</sup>Assistant Professor, Sreenidhi Institute of Science and Technology, Hyderabad, India

#### Abstract

Article Info Volume 81 Page Number: 5246 - 5251 Publication Issue: November-December 2019

Article History Article Received: 5 March 2019 Revised: 18 May 2019 Accepted: 24 September 2019 Publication: 25 December 2019 In most SoC development programs, FPGA prototyping has become widespread to some extent. This document is a short debate of four elements of the strategy of this sort. First, we examine the forces behind this trend and discuss what will be required in the future. Second, a brief overview is described of the traditional methods of code coverage verification, assertion-based verification, and functional coverage. Third, how the FPGA verification method is best incorporated into the general growth of the chips is examined. Lastly, a FPGA instrumentation method is implemented to measure coverage.

Keywords: FPGA, SoC, Prototyping, Lowpower, chip design.

#### I. INTRODUCTION

As structures grow progressively intricate also configuration cycles developsmallerthen shorter, insightful specialists also supervisors search on behalf of approaches to effort more intelligent not simply tougher. FPGA prototyping is solitary of those methods. This introduces another test to the structure and check groups. The test is the manner by which top to join the exertion that goes interested in an FPGA model hooked on the general confirmation activity. This document investigates the powers after the ongoing increment in FPGA prototyping, audits the customary confirmation procedures.Examines how FPGA prototyping canister be a piece of the check exertion alsoprovides instances of how to check rationale containerbe situated joined in the FPGA model. The thoughts exhibited in this broadsheet are basic yet incredible in delivering a superb plan with as meagre time and exertion as could reasonably be expected.

## II. FORCES BEHIND FPGA PROTOTYPING

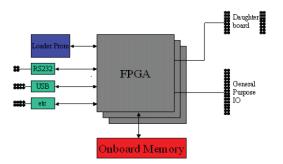

FPGA prototyping of aSoC configuration be able toprecede numerous structures. The whole gadget throughcompletely usefulness spoke to, explicit squares just or any mix in the middle. The FPGA may likewise be utilized as confirmation of the idea stage. This methodology has turned out to be well known for various reasons. Low hindrance of a section, a high level of reuse, programming combination, framework engineering approval, and execution observing are a couple of reasons that are investigated here. Not just has FPGAs themselves to turn out to be generally cheap yet in addition, the wealth of FPGA advancement stages has driven the expense down. Likewise, regardless of whether a custom board is grown, maybe with custom simple, an accomplished board house can create this in only weeks. So as to be most valuable, these stages must contain various things. To begin with, they should contain an FPGA that is sufficient in dimension and IO to contain mutually the structure beneath test and the supporting test and investigate highlights, for example, troubleshoot ports, rationale analyser associations and inserted following equipment. There might be situated a requirement on behalf of a stage that has different FPGAs. This is particularly helpful while the plan comprises IP that should remain secured. For this situation, a scrambled bit stream containerremains created on favour of a solitary FPGA that is practically difficult to figure out. Additionally, the stage ought to consume choices in place of outside remembrance. Though this won't be essentialon behalf of all structures it is alluring to limit the digit of stages a plan focus necessity keeps up. The measure of recollection is constantly a unique little something that never appears to be sufficient. The stage ought to likewise consume the greatest widely recognized physical boundaries executed on the sheet. RS-232 also universally useful TTL IO as a base. USB, Ethernet, as well as Fire wire remain likewise valuable. In conclusion, the stage ought to have a method for associating

a type of little girl pass to the motherboard. This is an approach toward broaden the highlights of the stage in a brisk also cheap way.

Figure 1. FPGA Verification Platform

Additional part of powerful&utilization of F.P.G\_A stages is the more level of recycle. Increasingly mind-boggling circuits and quicker plan recycles command that the mark creator embrace methodology of structure tostructure from demonstrated sub squaresas opposed to making without any preparation. It is then the planner's duty to comprehend the interfaces to the sub/squares all around personally. This should be possible by perusing the certification and finished reproduction. Genuine prototyping on the F/P/G/A is additional method for increasing comprehension of the IP. Most fashioners would confirm that really utilizing something is the most ideal approach to get familiar with the subtleties. Programming mix can be an extensive and more exertion job. Final product creator's anIMPjumpby an F.P.G.A stage is an approach to cover the equipment &programming exertion in a way that limits the measure of disposable technical code. The F/P/G/A stage can furnish the product creator with a somewhat precise, timepiece cycle exact improvement framework that is exceptionally valuable for building up the layer of programming that interfaces straightforwardly to the equipment. When a specific measure of programming is composed it ends up conceivable to assess the framework design. This incorporates sizes of the FIFO's or cradles, transport data transfer capacities and measure of code cosmos required. Altering the engineering dawn in the improvement can drastically affect the calendar so recognizing issues as ahead of schedule as conceivable is constantly alluring. To wrap things up, execution checking, particularly with the product included can be performed on the stage. For instance, it is anything but difficult to assess what number of processor guidelines per note is essential at this platform. This is valuable to figure out what working rates the structure needhappen or if different supercomputers or coprocessors are justified. Clearly tending to these variables right off the bat in the improvement cycle is an absolute necessity to keep up a quick spell to showcase. A fewer substantial purpose is that devising a stage that really plays out a capacity that can be gotten, heard or felt is of boundless worth. Most of the recreations on the planet

miss the mark concerning the effect of seeing something play out the direct. Audit of outdatedCertificationSystemstoget how FPGAs can help in aiding confirmation, it is suitable to consume a short exchange of check procedures. The following is a portrayal of inclusion-based confirmation, itemizing Declaration, Snap, Division and Qualified inclusion. Declaration established check is depicted and utilitarian inclusion is examined. Code inclusion is presumably the best utilized sort of capability to decide whether your check exertion is enough. Proclamation inclusion is just a proportion of how regularly each line, or articulation, in your structure is executed by the test system. Switch inclusion takes a gander at everyleft or schedule to decide whether the sign alterations. It might likewise incorporate information on if the sign rose or fell. Branch inclusion assesses every one of the divisions in the code also decides whether every branch is occupied. Contingent inclusion energies much further. It will see which condition makes the branch be taken. For instance, in the announcement "on the off chance that (an or b) at that point c", restrictive inclusion will gauge if "c" is executed on the grounds that both "an" and "b" are valid. Code inclusion is a decent proportion of how broad the test bench is nevertheless it truly enlightens small regarding the accuracy of the structure. A check designer can accomplish a high level of code inclusion without taking a gander at the detail of what the structure should do. It is likewise conceivable to accomplish your code inclusion metric deprived offsetting for pass/bomb situations. As it were, it is extremely a proportion of your upgrade however not really a proportion of your check. Useful inclusion is a check approach that has picked up in prevalence in the course of recent years. Here, the structure is exposed to enter that is obliged yet pretty much arbitrary. The check happens in one of two different ways. In the first place, affirmations are put in and around the structure that will signal mistakes on the off chance that they happen. This is particularly helpful for convention screens. Another, the payload or else yield of the structure is tested. The upside of useful confirmation is a check architect can run an enormous number of vectors through moderately tiny exertion in setting up the boost also the affirmations. It is conceivable to ensure utilitarian confirmations in local Verilog of VHDL however a few business items exist that permit the check designer to spare a lot of time. When utilizing practical check procedures, the activity of estimating inclusion isn't as straight onward as code inclusion. Code inclusion measurements be situated surely known also are the equivalent starting with single structure then onto the next. Not so for practical inclusion measurements. A plan useful inclusion must be characterized for every single task. The check would then be able to continue to run into that explanation however there is an abstract environment in figuring out what is 100% secured. Therefore, the nature of your confirmation is just comparable to your

useful inclusion spec. This is one of the shortcomings of this sort of confirmation. It is significant for the check architect to understand that most dark bugs occur because of various, disconnected things occurring in parallel. For example, a hinder happens in a bolted transport exchange. It is basic for the specialist to have a solid and strong creative mind when determining the utilitarian inclusion components. Reproduction of a similar bundle, again and once more, cannot uncover a concealed bug.

## III. FPGA VERIFICATION TECHNIQUES

Toward appropriately utilize FPGA prototyping; the confirmation designer must have an all-around arranged and painstakingly considered check plan. The check plan ought to unmistakably state which shares of the structure determination be exposed to code or else utilitarian inclusion also which shares resolve be practiced in FPGA. On behalf of those zones wherever FPGA is the primary centre, a point by point portrayal of how this will be cultivated is required. It might appear the moderate way to deal with overlooking the FPGA

model when confirming your structure yet when you are attempting to lessen time to showcase it bodes well to approach confirmation comprehensively. Exertion isn't in boundless booting.It is smarter to spread on exertion in unverified territories than to copy it checking very similar belongings in various methods. The conventional coordinated experiment check must focus on the parts of the structure that can't stand precisely prototyped in the FPGA. Practically the majority of the structure for-test regions drop in this class. Additionally, the recollections utilized in the plan resolve most likely remain not quite the same as the inserted recollections accessible in the FPGA. The boundary to these recollections ought to be testedthrough customary strategies. Whatever extra IP that is not the same as otherwise not existing in the FPGA ought to remain completely assessed in reproduction. PLLs as well as DLLs fall hooked on this classification. As ensure a large portion of the physical boundary IP. The following is a table that condenses how unique part of the plan ought to be checked.

|                             | Traditional Verification | FPGA Prototype |

|-----------------------------|--------------------------|----------------|

| Payload                     |                          | Х              |

| Software Compatibility      |                          | Х              |

| Real-time Performance       |                          | Х              |

| Embedded Memory             | X                        | Х              |

| Built in Self Test (BIST)   | X                        |                |

| Embedded IP Interface (PLL) | Х                        |                |

| IO Pad operation            | Х                        |                |

| Reset/Power up sequence     | Х                        | Х              |

#### IV. IMPLEMENTED CONFIRMATION IP

A larger amount of advancement is to really actualize confirmation IP in the FPGA. This turns out to be most valuable onceF/P/G/A be utilized in a type of live condition. Transport screens that form the convention, counts that monitor various exchanges and statement blunder summers could be combined right in the F/P/G/A. Framework could be practiced for broadened timeframes and attend, the adders and counting's can be inspected. Afterward the outcomes are gathered, explicit examinations could be achieved to statement any zones that did not become secured. This work will work

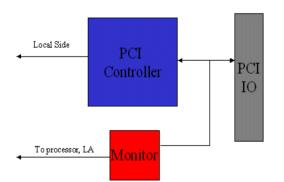

complete a straightforward yet nitty gritty model. Following are a few instances of in what way to execute check I/P in the F/P/G/A model. Primary model is a P/C/I transport screen that is viewing the P\_C\_I transport&classification if particular kinds of gets to happen. It might monitor what number of each sort of access happens too. For example, soundtrack the greatest No of information moves throughout eruption cycle would-be helpful aimed at confirmation architect to know. In the event that enormous blasts don't happen, he can attempt to usual up a particular test or feed the data to the confirmation group so practice it's in a re-enactment.

Figure 2 P/C/I Bus Monitor

Additional cause that helpful F PGA confirmation method is a first in first out profundity screen. In interchanges frameworks, the profundity of the FI\_FOs is a significant limitwhen thinking about framework execution. On the off chance that they are 2 little overruns' happen bringing about loss shipment. On the off chance that they are excessively huge, at that point you are squandering silicon zone and in this manner cash. It is even conceivable to log mistake condition, for example, perusing a vacant FIFO or keeping in touch with an entire one. The last guide to talk about is a processor ongoing screen. This requires the help of programming however can demonstrate to be an extremely valuable component. The thought is to put an order in the processor's inert schedule that additions equipment register each time the product goes through the inactive circle. Clearly the additional time the product occupies in the inactive circle the extra the record will increase. Alternative, a freerunning counter is executed in equipment as well as unaffected through the product. At the point when the free-running counter moves completed the incentive in register increased by the product is spared off, likely in memory or perhaps conveyed off the FPGA. A record of these qualities' container be explored to decide a past filled with the processor inert time. It would be genuinely simple to execute an alert situation if the inactive worth at any point arrived at a specific limit. This can be estimated under various traffic burdens to give the framework configuration group an awesome comprehension of how programming and equipment associate. These systems in the long run require the information to be perused out of the FPGA. This can be cultivated in various ways. In the event that the framework permits, the application possibly will be halted also the processor itself might peruse inner registers as well as convey the outcomes concluded its investigate port. This is a decent method since it permits the measure of time the example is dynamic to be measured. Additional path is to make a port utilizing extra sticks on the FPGA. These pins container be associated with a rationale analyser that provisions the information as it is gushed out or else a troubleshoot port like a processor investigate port be able to be developed. On account of the last mentioned, care must be taken to keep up information respectability when information is accessible yet the troubleshoot port isn't overhauled. A third route is to utilize the FPGA inserted rationale analyser highlights to develop a blend of the initial two. The counter recordsotherwisereminiscence substance container be indicated as test focuses also guided hooked on the installed LA. Along these lines, the client container question the inward enlists whenever. Approval is concerned about demonstrating a structure's consistency and continuation as to customer requirements. This is where you are actually making an item adjustment and approving against the customer's preconditions.

- During the improvement phase of detail, the recognizable proof of check action is done parallel. This empowers the architect to ensure that the determination is certain. So a test specialist can begin definite test plan and strategies. Any adjustments in the detail ought to be imparted.

- Identifying the best way to deal with lead confirmation, characterize estimation strategies, required assets, apparatuses, and offices.

- The finished confirmation plan will be investigated with the structure group to recognize issues before concluding the arrangement.

- Here we plan an SGMII IP check engineering is built and this design is confirmed with test information outlines.

- The on-chip processor is planned and actualized with RAM, RX, TX, Trigger circuit.

- Packet age and bundle checking are seen with Xilinx Vivado programming on structured engineering.

- The IP has 1G throughput in every interface is confirmed on planned engineering.

- GMII Tx, GMII Rx, PHY Tx, PHY Rx are to be actualized.

- For confirmation purposes, running all interfaces with full throttle needs 4G information rate.

- To utilize same DDR for both Tx and Rx stockpiling purposes we have to run DDR3/4 at 333MHz and 16-piece interface and checked this structure on actualized engineering.

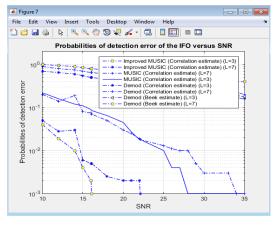

# V. TEST RESULTS

Field-programmable door cluster prototyping (FPGA prototyping), likewise alluded to as FPGA-basedprototyping, ASIC prototyping or framework on-chip (SoC) prototyping, is the technique to prototypesystem-on-chip and application-explicit incorporated circuit plans on FPGAs for equipment confirmation and early programming improvement.

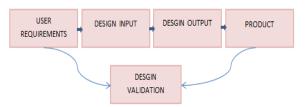

Figure 3. Schematic of prototype

Figure 4. Different methods related to prototype

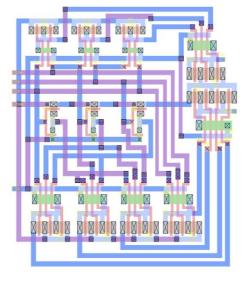

Figure 5. Waveform representation of prototype

FPGA prototyping is a settled method for confirming the usefulness and execution of use explicit ICs (ASICs), application-explicit standard items (ASSPs) and framework on-

chips (SoCs) by porting their RTL to a field programmable door exhibit (FPGA).

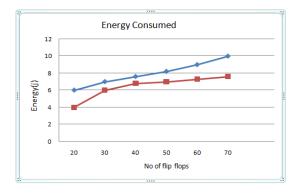

Figure6. energy requirements existed vs. proposed

Power-analysis attacks are typical examples of side-channel attacks that have been demonstrated to be effective against implementations without special countermeasures. The flexibility of FPGAs is an important advantage in real applications but also in lab environments.

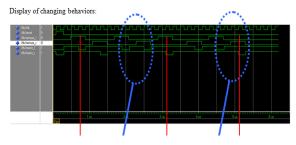

#### VI. FUTURE IMPROVEMENTS

Many things can be done to improve this system or have some more fun with it:

- arbitrary turning direction when hitting obstacle on both sensors simultaneously

- arbitrary turning distance (degree)

- adding photo sensors and add light chasing/avoiding behaviour

- random number of collisions for behaviour change

- behaviour is memorized when machine is restarted (not reset)

- adding more behaviour, etc.

**Table: 2 Area Analyses**

|           | Unprotected<br>FFTs | protected    | existed method | Pro |

|-----------|---------------------|--------------|----------------|-----|

| Slices    | 15037               | 21811 (1.45) | 23378 (1.55)   |     |

| Flip-Flop | 11407               | 16533 (1.45) | 14727 (1.29)   |     |

| LUT-4     | 27830               | 40805 (1.47) | 44273 (1.59)   |     |

#### VII. CONCLUSION

FPGA prototyping is a methodology that can significantly help the improvement group in delivering a quality structure in a time period that lessens the immeasurably significant time to showcase. This broadsheet looks to address the difficulties just as feature the advantages of such a methodology. Straight forward, straightforward models are introduced to express the methodology in an unmistakable and proficient way.

#### REFERENCES

- [1] Saikumar, K., Rajesh, V., Ramya, N., Ahammad, S. H., & Kumar, G. N. S. (2019). A deep learning process for spine and heart segmentation using pixel-based convolutional networks. Journal of International Pharmaceutical Research, 46, 278- 282. Retrieved from www.scopus.com.

- [2] Ahammad, S. H., Rajesh, V., Saikumar, K., Jalakam, S., & Kumar, G. N. S. (2019). Statistical analysis of spinal cord injury severity detection on high dimensional MRI data. International Journal of Electrical and Computer Engineering, 9(5), 3457-3464 doi:10.11591/ijece.v9i5. pp3457-3464.

- [3] Rajesh, V., Saikumar, K., & Ahammad, S. K. H. (2019). A telemedicine technology for cardiovascular patient's diagnosis feature using knn-mpm algorithm. Journal of International Pharmaceutical Research, 46, 72-77. Retrieved from www.scopus.com

- [4] K. Sai Kumar,Y Sri Chakrapani,Dr. M.Kamaraju "Implementation of Low Power Ultrasonic Phased Array Using ZYNQ-SoC" IRACST - International Journal of Computer Science and Information Technology & Computer (IJCSITS), ISSN: 2249-9555 Vol.6, No4, July-August 2016.

- [5] Dr.D.R.V.A.Sharath Kumar, AyeeshaTaranum and G.Sujatha, published the paper in the U.G.C Journal (IJSRCSAMS) on "Advanced Image Restoration for Headway Video Recorders" in volume 2 issue 6 in the month of December 2013.

- [6] Dr.D.R.V.A.Sharath Kumar, V.Shivaraj Kumar and Sridhar Goud, published the paper in the U.G.C Journal (IJRCEE) on "Migration for Secure Data Acquisition Systems" in the month of March 2014.

- [7] Zeineb Bel Hadj Amor, Laurence Pierre, Dominique Borrionr, "System-on-Chip Verification: TLM-to-RTL Assertions Transformation", 14516132, June 30 2014- July 3 2014.

- [8] Basavaraj Mudigoudar," FPGA Prototyping for fast and efficient verification of ASIC H.264 decoder", The University of Texas at Arlington, May 2006.

- [9] .Nirav R. Parmar, Vrushank M. Shah "Study of Various Ways to Optimize ASIC Design Cycle timings", ISBN: 978-960-474-155-7

- [10] S. Brown and J. Rose, "FPGA and CPLD architectures: a tutorial", IEEE Design & Test of Computers, vol. 13, issue 2, pp. 42 – 57, Summer 1996.

- [11] P.-A. Hsiung, "Hardware-software timing co-verification of concurrent embedded realtime systems", IEE Proceedings on Computers and Digital Techniques, vol. 147, issue 2, pp. 83 – 92, Mar 2000.

- [12] Y.Sungjoo et al., "Fast hardware-software co-verification by optimistic execution of real processor", Proceedings of IEEE Conference and Exhibition on Design, Automation and Test, pp. 663 – 668, Mar 2000.

- [13] Rui Wang, "Reuse issues in SoC verification platform", Pages:

685 688 Vol.2, ISBN : 0-7803-7941-1, 26-28 May 2004

[8].http://www.soccentral.com/PrintPage.asp?P

assedEntryID=18241

- [14] Steve Brown, "TLM Driven Design and Verification", white paper, www.cadence.com,June 2009.

- [15] http://www.testbench.in/AS\_00\_INDEX.

- [16] .ZocaloTech,www.zocalotech.com/files/ass ertionverification\_whitepaper.pdf.